Intel は、「Intel 4」E-Core チップの PowerVia として知られる次世代のバックサイド パワー デリバリー テクノロジをまもなく示します。

Intel PowerVia のデモが近日公開されチップ背面にあるスタンドアロンモジュールによる電力供給の利点を示す

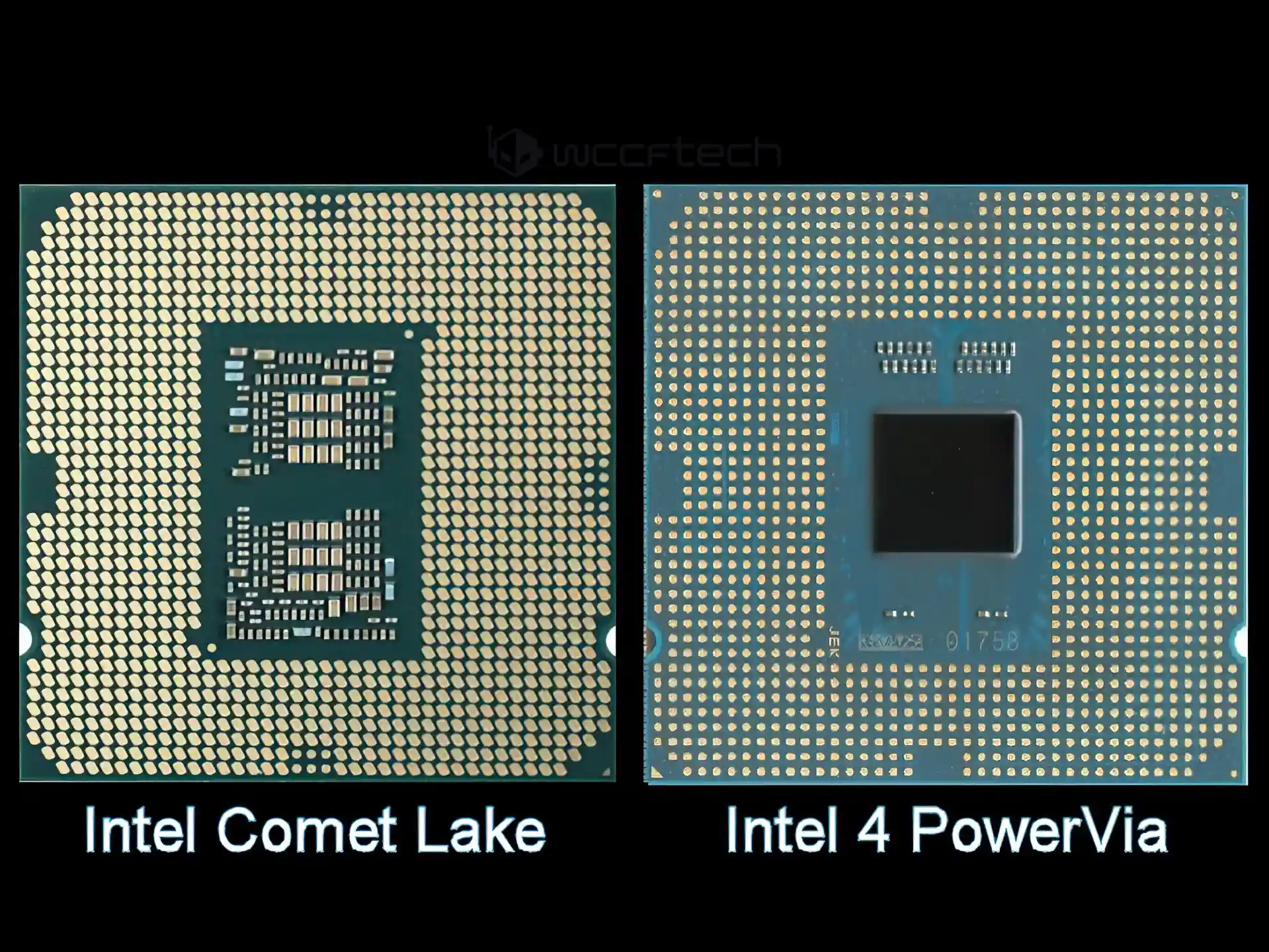

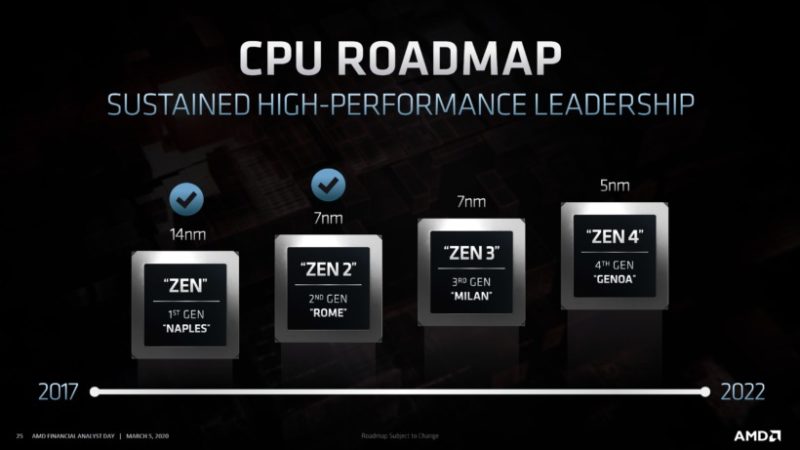

Intel の PowerVia のこの実装の最初の外観は、VLSI によってTweetされており、6 月に始まる 2023 年の VLSI に関するシンポジウムでデモが行われる予定です。Twitterの中で、VLSIは、「Intel 4」プロセスノードを利用し、オールE-Core実装を搭載していると言及されているチップの裏側にIntelがPowerViaを実装していることを示しています。

#VLSI2023 Highlight paper T1-1 “E-Core Implementation in Intel 4 with PowerVia (Backside Power) Technology” – Intel Corp.

Intel reports a high-yielding backside power delivery technology, PowerVia Technology*, and Intel E-Core Implementation in PowerVia Technology. pic.twitter.com/0us9rbUvQr— IEEE Symposium on VLSI Technology and Circuits (@VLSI_2024) May 2, 2023

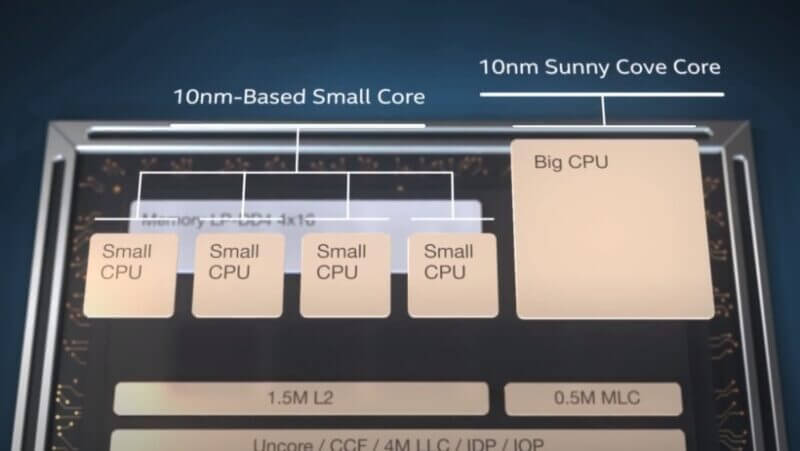

Intel 4 チップは、その正方形の形状により、古い LGA1151/LGA1200 設計に基づいているように見え、パッケージの下にセカンダリ ダイがあります。これは通常、大量の小さなトランジスタが見られる領域ですが、それらの大部分は PowerVia テクノロジに置き換えられています。E-Core の実装が「Intel 4」に基づいていることを考えると、Meteor Lake の E-Core を強化する今後の Crestmont アーキテクチャに基づいている可能性があります。

さらに、セル使用率は、チップ内の 2.9mm2 の領域で、Intel PowerVia テクノロジが最大 90% の使用率に達する可能性があることを示し、使用率が向上するだけでなく、同じチップで 5% 高いクロックを実現する IR ドロップの減少により、わずかなクロック速度の向上にもつながります。

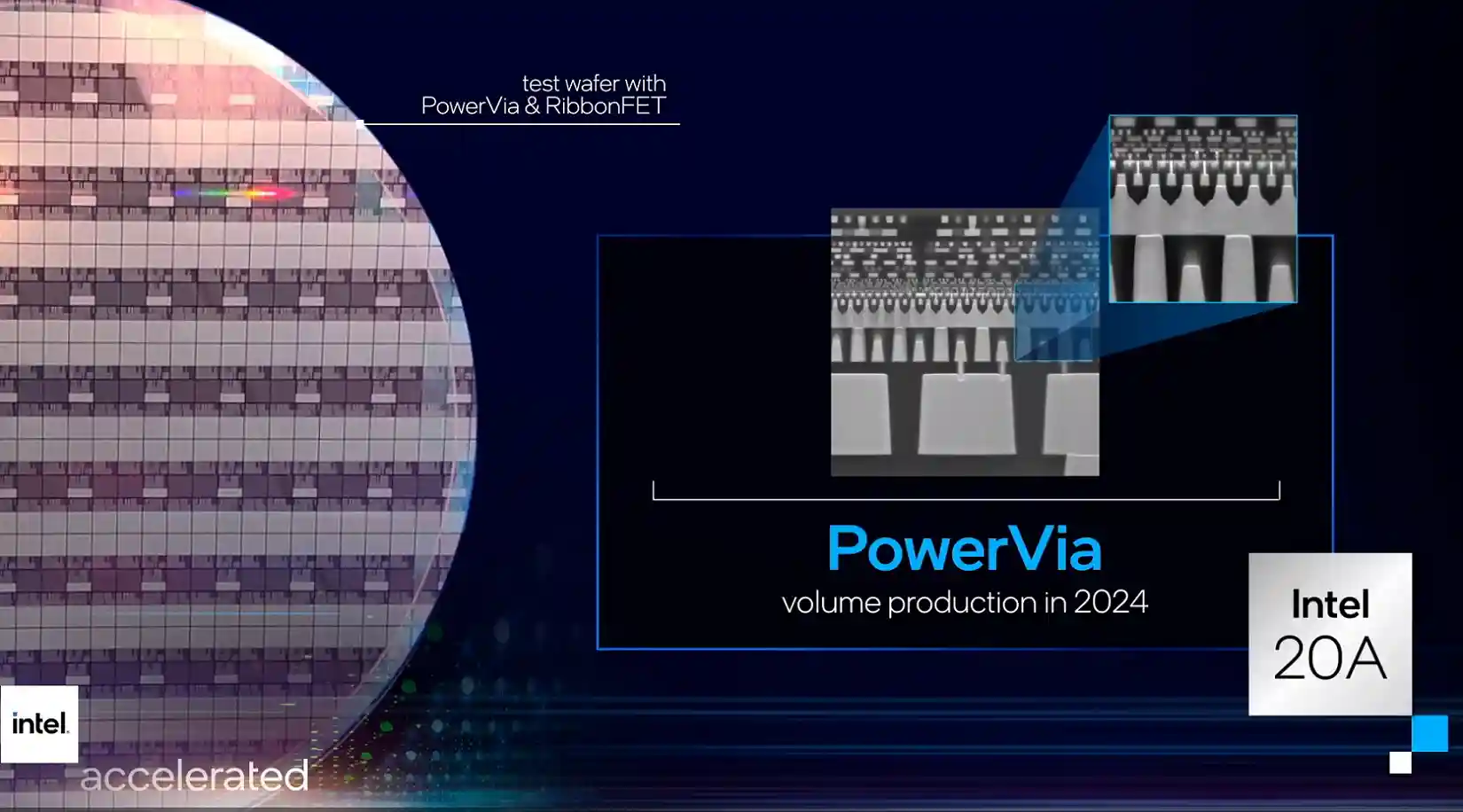

さらに興味深いことに、VLSI は、これは高収量の設計であるが、少なくとも Arrow Lake または Lunar Lake 世代までは登場しないと述べ、その理由は、PowerVia と RibbonFET が20A と 18A のプロセス ノードによってコンシューマ レベルのチップに採用されようとしているからです。最初の PowerVia チップは、2024 年までに量産に入ると言われています。

以前から、PowerVia は、シリコン アーキテクチャに見られる相互接続内のボトルネックの問題を解決するために裏側で機能する電力供給プロセスであることがわかっています。これは、PowerVia が利用可能になったときに解決すべき一般的な問題です。データ通信信号と電力をトランジスタ層の最上部に伝送するインターコネクトの代わりに、Power Via はシリコン ウエハーの裏面に直接供給し、同時にウエハーの最上部で信号を伝送します。

以前から、PowerVia は、シリコン アーキテクチャに見られる相互接続内のボトルネックの問題を解決するために裏側で機能する電力供給プロセスであることがわかっています。これは、PowerVia が利用可能になったときに解決すべき一般的な問題です。データ通信信号と電力をトランジスタ層の最上部に伝送するインターコネクトの代わりに、Power Via はシリコン ウエハーの裏面に直接供給し、同時にウエハーの最上部で信号を伝送します。

PowerVia が何をするのか、電力供給の面で状況を変えることができるテクノロジのように思え、今後数か月のうちに実際に動作するのを見るのが待ち遠しいです。

(Source:wccftech)

この記事へのコメントはありません。