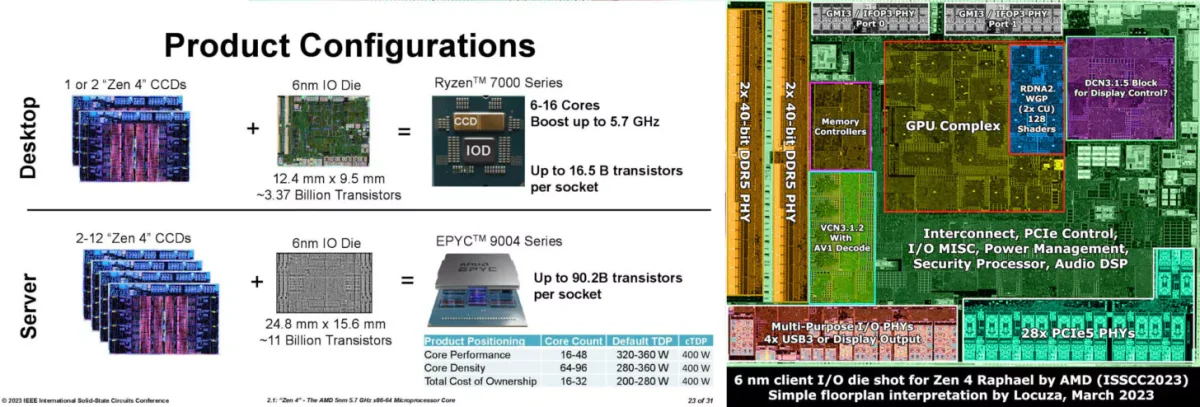

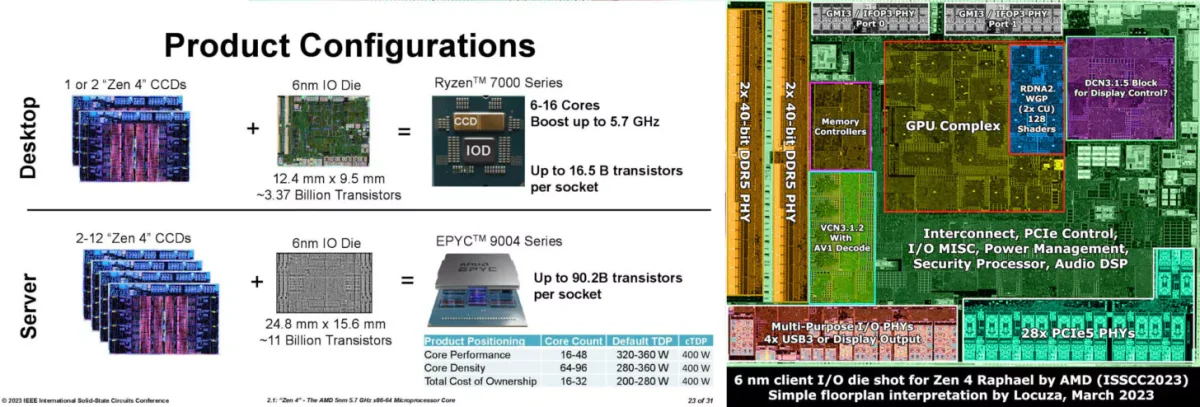

同社が公開した画像の 1 つは、次世代の 3D V-Cache 向けの新しい I/O ダイの初見でした。この新しい I/O ダイは、最新の Ryzen 7000 X3D “Raphael” CPU に搭載されています。

AMD は、非 X3D パーツに対して L3 キャッシュにさらに追加し、1 つのチップレットで最大 96 MB のサイズをもたらし、7nm プロセス ノード テクノロジに基づいています。L3 キャッシュは、5nm Zen 4 コア コンプレックス ダイ (CCD) 上にスタックされます。次世代のキャッシュ ダイは小さくなりますが、同じトランジスタ数が維持されます。ただし、トランジスタ密度は元の 114.6 MTr/mm² から 130.6 MTr/mm² に増加し、2.5 TB/s のより高い帯域幅に達し、5800X3D 設計から 25% の改善に相当します。

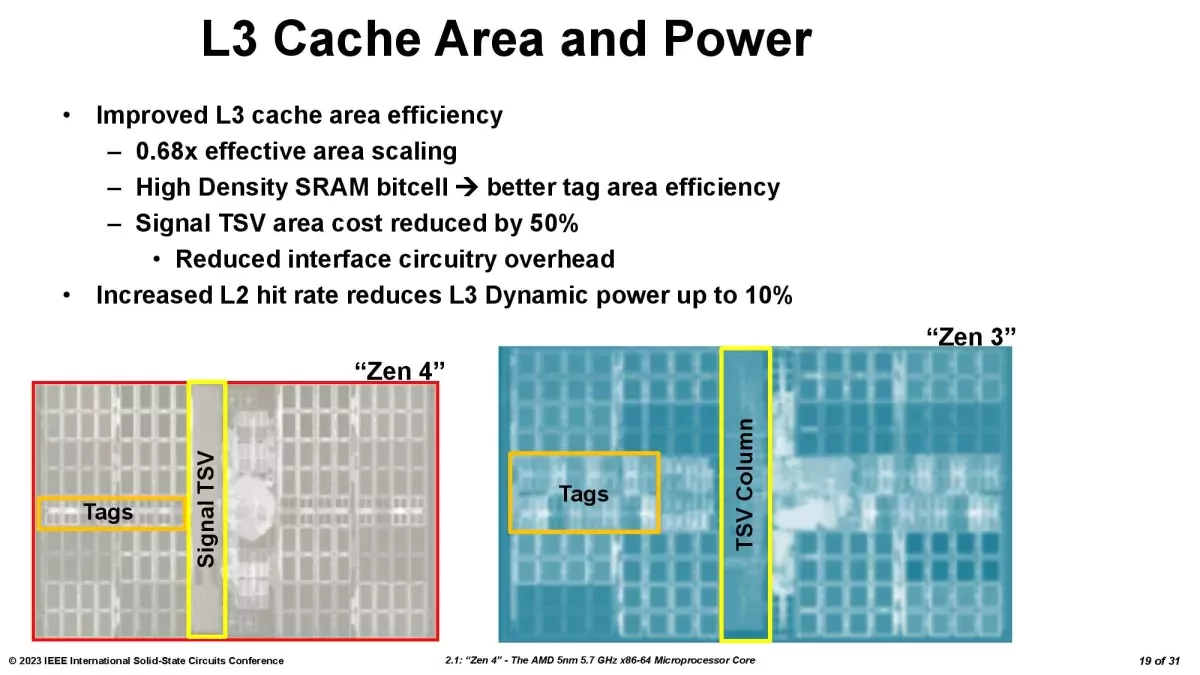

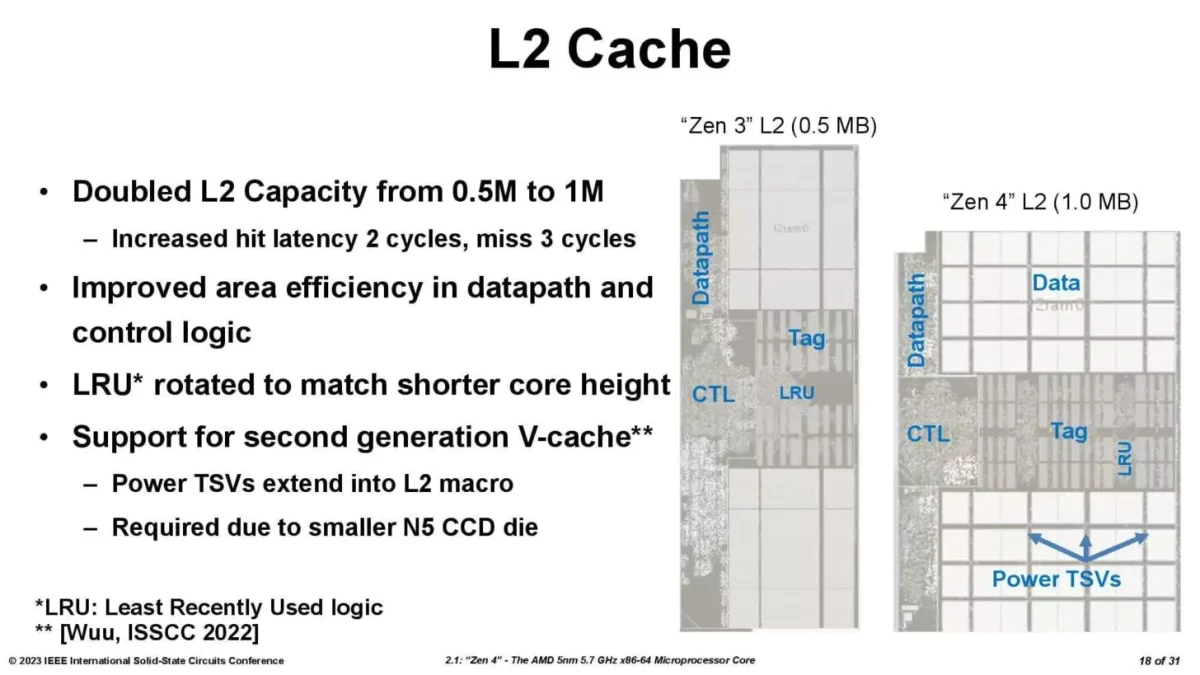

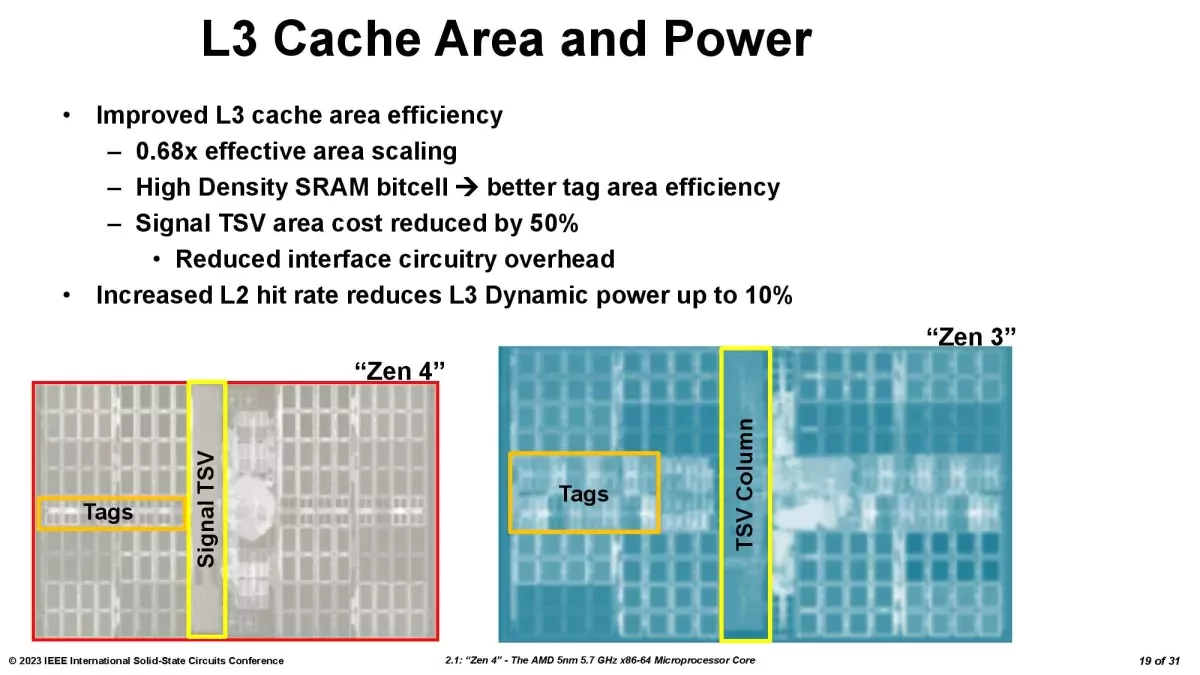

同社はThrough Silicon Vias (TSV) 接続領域を半分のサイズに調整しました。Zen 4 の CCD は現在、Ryzen 7000 X3D コンシューマ プロセッサと EPYC 9004 サーバー/ワークステーション CPU に搭載されています。現在、I/O ダイは、リリース時にコンシューマモデルとサーバー モデル用に変更され、2 つのグローバル メモリ インターコネクト ポートを備えているため、3 つの CCD を同時に使用する構成が不要になります。

新しいダイは、128 ビットの DDR5 物理層 (PHY) と、32 ビット チャネルあたり 8 ビットの 32 ビット エラー訂正コード メモリ (ECC) も提供し、PCIe 5.0 物理層の 28 倍であり、これは PCIe 5.0 よりも 4 少ない。オンデマンドの Zen 1/2/3 計算統合、または cIOD。最後に、チップレットは 128 のシェーダー コアを提供する予定です。

(Source:wccftech)

コメント (0)

トラックバックは利用できません。

この記事へのコメントはありません。