(adsbygoogle = window.adsbygoogle || []).push({});

他の詳細は、既存の Zen 3 CCD ですでに機能している TSV の上にある 64 MB の L3 キャッシュが単一の 3D V-Cache スタックに組み込まれていることを確認し、キャッシュは、既存の 32 MB の L3 キャッシュに追加され、CCD ごとに合計 96 MB になります。最初の製品には、チップレットごとに 1 つの 3D V-Cache スタックが含まれるため、最上位の Ryzen SKU で合計 192 MB のキャッシュを見ています。ただし、AMD は、V-Cache スタックは最大 8-hi まで使用できると述べています。これは、技術的には、単一の CCD が、Zen 3 CCD ごとに 32 MB のキャッシュに加えて、最大 512 MB の L3 キャッシュを提供できることを意味します。

I’m trying to confirm that the TSV sites were clearly visible from the fist chip shots we have seen of a Zen 3 CCD.

These are shots from @FritzchensFritz, I did just add the notation. pic.twitter.com/rlm17BOQk5

— Andreas Schilling (@aschilling) June 1, 2021

AMD は、Zen 3 CCD と V-Cache を間引いて、コアと IOD の間で高さを変えるのではなく、現在の Zen 3 プロセッサと同じになるようにしました。V-Cach は CCD L3 キャッシュの上にあるため、コアの熱出力には影響せず、電源投入時のティックは最小限です。

AMD は、チップレット アーキテクチャ ベースの CPU 向けの次世代 3D スタッキング デザインも発表しました。このテクノロジーは、複数の IP を互いに積み重ねることが期待されていますが、AMD によって展示されたプロトタイプには、64 MB の L3 SRAM を備えた 3D V-Cache を備えた Ryzen 9 5900X が含まれていました。

プロトタイプは、6mmx6mm (36mm2) の 3D パッケージ CCD の隣にある標準の Zen 3 CCD を備えています。CCD のサイズは以前と同じですが、CCD の上に 64 MB のキャッシュを備えた別のパッケージがあり、Zen 3 CCD に既に搭載されている 32 MB の L3 キャッシュに追加されます。

これは、CCD ごとに合計 96 MB の L3 キャッシュ、または Ryzen 9 5950X CPU 全体で合計 192 MB の L3 キャッシュに切り上げられます。3D V-Cache は、いくつかの TSV を介して CCD に接続されます。AMD は、このハイブリッド ボンド アプローチにより、200 倍以上の相互接続密度を実現し、全体の効率を 3 倍にすると述べています。

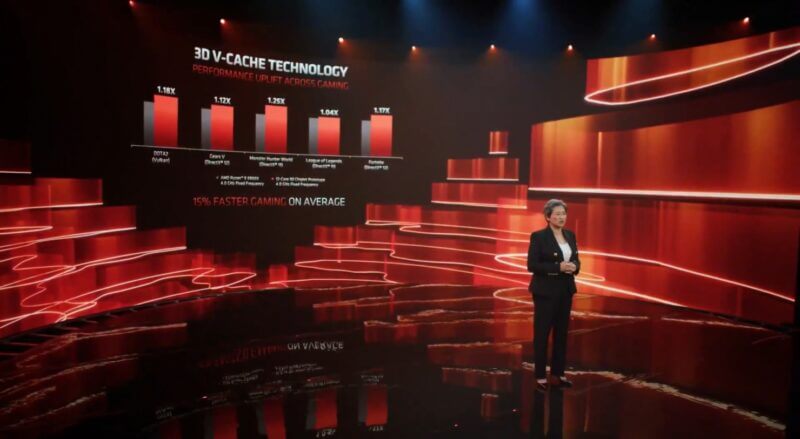

AMDはこのプロトタイプのデモまで行った. Ryzen 9 5900X プロトタイプは Gears V を実行していて、ゲームのキャッシュ サイズが増加したおかげで、パフォーマンスが最大 12% 高速になりました。平均して、AMD は 3D V-Cache 設計によりパフォーマンスが 15% 向上すると主張しています。各 V-Cache スタックは、最大 2 TB/秒の全体的な帯域幅を提供します。AMD は、Intel の Rocket Lake デスクトップ CPU ラインナップと比較して、優れたゲーミングパワーをすでに提供しているため、この追加のパフォーマンス バンプは、Intel が次世代の Alder Lake CPU に賭けてきたすべてを打ち砕く対策でありその可能性があります。

AMD 3D Chiplet Technology: A packaging breakthrough for high-performance computing.

— AMD (@AMD) June 1, 2021

さらにはAMDが間違いなくZen 4 Ryzen CPUにこの技術を搭載し、最近の噂で報告されているように、今後のZen 3搭載のRyzen & EPYC Milan-Xとスタックされた3D V-Cacheチップレットをパッケージ化するために一歩先を行きます。