これまでのところ、NVIDIA GeForce RTX40シリーズグラフィックスカードは新しいATX3.0準拠の12PV HPWR16ピンコネクタを採用し、新しいPCIe Gen5電源コネクタインターフェイスを介して最大600Wの電力を引き出すことができます。この電源コネクタは、GeForce RTX 3090Tiグラフィックスカードにすでに搭載されており、現在、トリプル8ピンアダプタを介して最大450Wの電力を引き出すことができます。ただし、PCIe Gen 5.0に完全に準拠するための別の側面があり、それがインターフェイスコネクタ自体です。

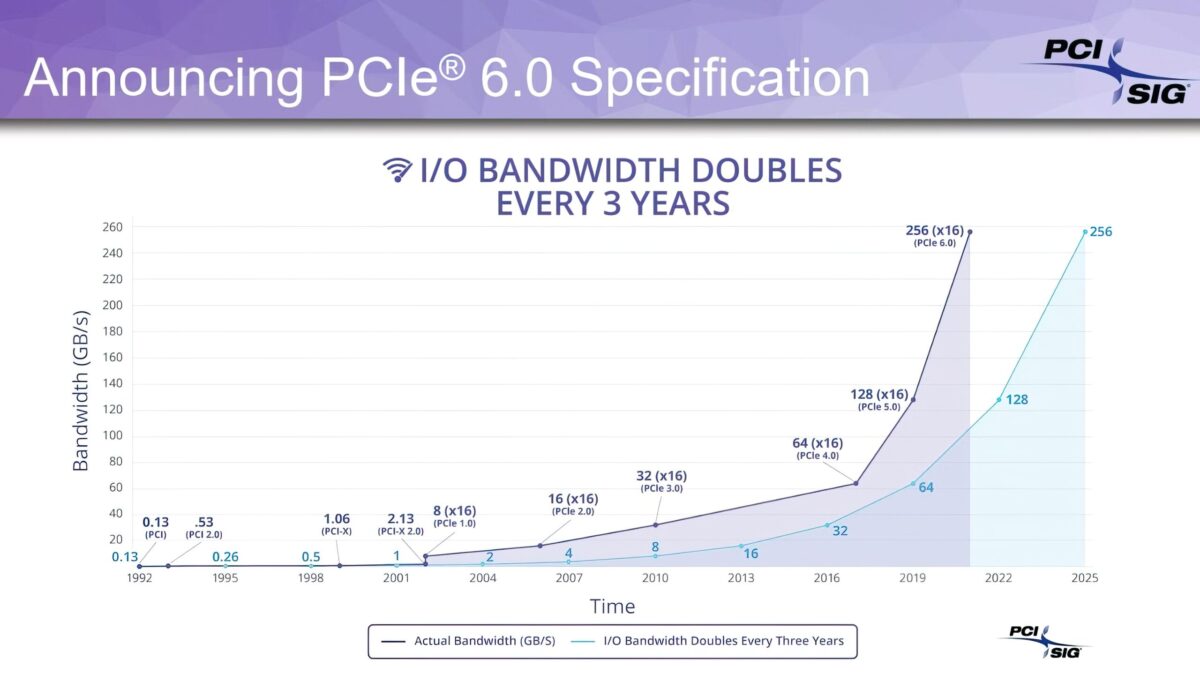

現在、最新のグラフィックカードはPCIe Gen4.0プロトコルを介してCPUと通信します。PCIe Gen 4.0プロトコルでは、合計64 GB/sおよび32GB/sの双方向帯域幅が可能です。しかし、IntelとAMDの最新のプラットフォームは、まったく新しいPCIe Gen5.0インターフェイスプロトコルをサポートしています。この新しい標準では、合計で最大128 GB / s、双方向帯域幅が64 GB/sになります。これは基本的に帯域幅を2倍にしますが、今後のグラフィックカードまたは少なくともAD102GPUに基づくハイエンドのGeForce RTX 40グラフィックカードは、PCIe Gen5.0インターフェイスをまだ備えていないようです。

Kopite7kimiからのツイートに基づいて、今後のGeForceRTX40ラインナップはPCIe Gen4.0プロトコルを保持します。これは、Hopper GPUが搭載されているHPCセグメントでホッピングしているにもかかわらず、次世代標準にホッピングしないというNVIDIAによる大胆な動きです。新しいプロトコルを最初に利用することになります。サーバーは多くの帯域幅を必要とし、Gen 5.0プロトコルがそれらの環境に役立つため、HPCラインナップがそれを備えていることは理にかなっています。消費者に関しては、PCIe Gen 5.0インターフェイスは帯域幅が広すぎて、現在のGPUはまだPCIe Gen4.0インターフェイスを完全に確立していません。

現在、PCIe Gen 4.0を使用することは、Gen 3標準に切り替えるときにRadeon RX6500およびRX6400シリーズの場合のように、より低いレーンが装備されている場合にボトルネックを心配する必要がないエントリーレベルのラインナップに適しています。最終的に必要なグラフィックス帯域幅よりも少なくなり、PCIe Gen 4.0準拠の標準と比較してパフォーマンスが低下します。ハイエンドのラインナップがGen 4.0標準に飢えていない場合、ローエンドのラインナップは最大しきい値に達するにはほど遠いです。これまでのところ、NVIDIAが今後のRTX40シリーズカードでPCIe Gen 4.0を本当に保持するかどうかは定かではありませんが、マーケティングが新しいカードにPCIe Gen 5.0のロゴを付けるのと同じように、変わる可能性があります。

現在、PCIe Gen 4.0を使用することは、Gen 3標準に切り替えるときにRadeon RX6500およびRX6400シリーズの場合のように、より低いレーンが装備されている場合にボトルネックを心配する必要がないエントリーレベルのラインナップに適しています。最終的に必要なグラフィックス帯域幅よりも少なくなり、PCIe Gen 4.0準拠の標準と比較してパフォーマンスが低下します。ハイエンドのラインナップがGen 4.0標準に飢えていない場合、ローエンドのラインナップは最大しきい値に達するにはほど遠いです。これまでのところ、NVIDIAが今後のRTX40シリーズカードでPCIe Gen 4.0を本当に保持するかどうかは定かではありませんが、マーケティングが新しいカードにPCIe Gen 5.0のロゴを付けるのと同じように、変わる可能性があります。

PCIe Gen5.0およびPCIe Gen4.0のサポートとは別に、NVIDIAは、CUDAコアがAda Lovelaceアーキテクチャ内に配置される方法にも大きな変更を加える予定です。GeForce RTX 40シリーズのGPUは、Ampereの単純なCUDAコア向上であるだけでなく、まだ詳細に説明されていない一連の新しい混合精度コアを含めることができます。ラインナップはまだ数ヶ月先ですので、随時変更される可能性がありますのでお知らせしていきます。

| GPU | TU102 | GA102 | AD102 |

|---|---|---|---|

| Flagship SKU | RTX 2080 Ti | RTX 3090 Ti | RTX 4090? |

| Architecture | Turing | Ampere | Ada Lovelace |

| Process | TSMC 12nm NFF | Samsung 8nm | TSMC 4N? |

| Die Size | 754mm2 | 628mm2 | ~600mm2 |

| Graphics Processing Clusters (GPC) | 6 | 7 | 12 |

| Texture Processing Clusters (TPC) | 36 | 42 | 72 |

| Streaming Multiprocessors (SM) | 72 | 84 | 144 |

| CUDA Cores | 4608 | 10752 | 18432 |

| L2 Cache | 6 MB | 6 MB | 96 MB |

| Theoretical TFLOPs | 16 TFLOPs | 40 TFLOPs | ~90 TFLOPs? |

| Memory Type | GDDR6 | GDDR6X | GDDR6X |

| Memory Capacity | 11 GB (2080 Ti) | 24 GB (3090 Ti) | 24 GB (4090?) |

| Memory Speed | 14 Gbps | 21 Gbps | 24 Gbps? |

| Memory Bandwidth | 616 GB/s | 1.008 GB/s | 1152 GB/s? |

| Memory Bus | 384-bit | 384-bit | 384-bit |

| PCIe Interface | PCIe Gen 3.0 | PCIe Gen 4.0 | PCIe Gen 4.0 |

| TGP | 250W | 350W | 600W? |

| Release | Sep. 2018 | Sept. 20 | 2H 2022 (TBC) |

(Source:wccftech)

コメント (0)

トラックバックは利用できません。

この記事へのコメントはありません。