(Source:Tom’s Hardware)

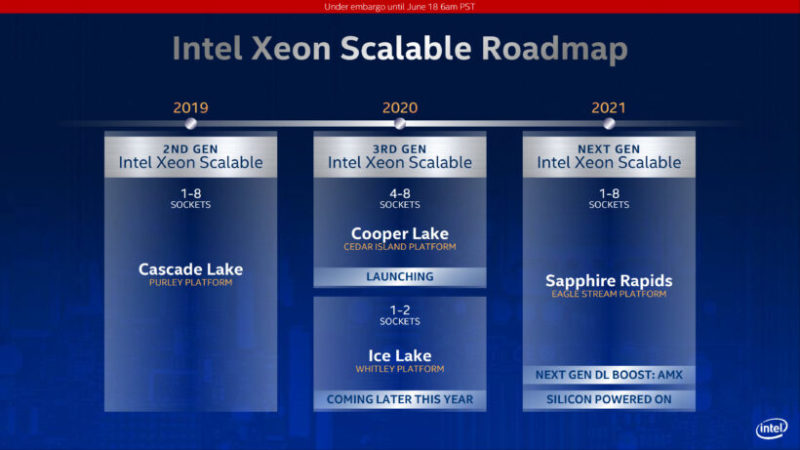

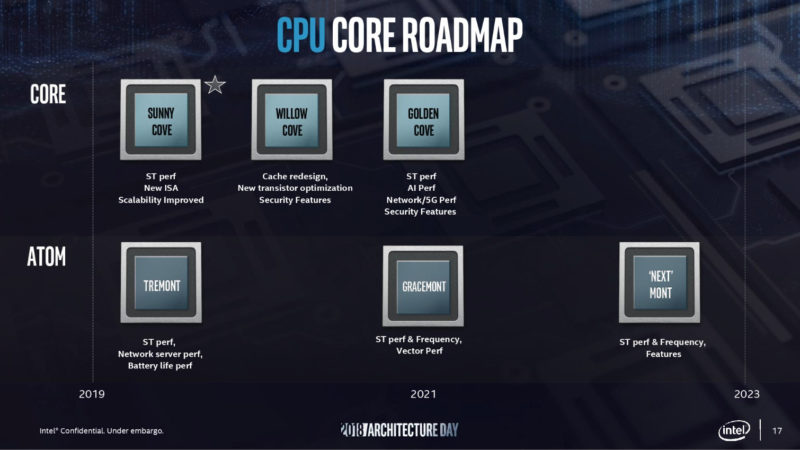

TwitterのInstLatX64(@InstLatX64)氏の投稿によると、Tieger Lake-UはL3 cacheが増量され、12MBになるそうです。Tiger Lake-Uは4コアなので、コアあたり3MBのL3 cacheということです。またTiger Lake-Uが4コア/8スレッドであること、現在姿を現しているEngineering Sampleが3.40GHzまで動作することが明かされています。さらには、命令セット周りの変更もあるようです。InstLatX64氏はall AVX512と記載しています。しかし、AVX512_bfは有していないように見えます。これはbfloat16をサポートする次世代Xeon Cooper Lakeがサポートするものだからです。以前にあった上のIntelのスライドには、Sunny CoveはSingle-thread performanceの向上、新たなISA、Scalabilityの向上が謳われています。その次のWillow CoveはCacheの再設計、新しいトランジスタ最適化、セキュリティ機能が挙げられています。そしてその次のGolden Coveになると再びSingle-thread performanceの向上があり、加えてAI性能やネットワーク/5G性能、セキュリティ機能などの項目が並んでいます。

Tiger Lake世代はWillow Cove世代のCPUコアになるというのが大勢の見方です。今回L3 cache容量が2MB/core→3MB/coreとなったことは、まさにWillow Coveの掲げる「Cacheの再設計」にあたります。そしてAVX512関連命令の新たな追加です。正直関連する命令が多すぎて正直どれがどれだかというところにInstLatX64氏の当該ツイートについているリプライを見るとどのProcessorがどこまでのAVX512命令を持っているかをわかりやすく図にしている方がいらっしゃいました。基本となるのがSkylake-Xで、ここからいろいろと追加が行われるようです。以下のような関係となるようです。

| CPU core | AVX512 instruction set |

|---|---|

| Skylake-SP | AVX512F, AVX512CD, AVX512BW, AVX512DQ, AVX512VL |

| Cascade Lake-SP | Skylake-SP+AVX512_VNNI |

| Cooper Lake-SP | Cascade Lake+AVX512_BF16 |

| Cannon Lake | Skylake-SP+AVX512_VBMI, AVX512_IFMA |

| Ice Lake | Cannon Lake+AVX512_VNNI, AVX512_VBMI2, AVX512_BITALG, AVX512_VPOPCNTDQ, AVX512_GFNI, AVX512_VPCLMULQDQ, AVX512_VAES |

| Tiger Lake | Ice Lake+AVX512_VP2INTERSECT |

確認してみると、Ice Lake相当が備えている命令はすべて備えているように見え、一方でAVX_512BF16は探しても見つかりませんでした。またAVX512_VP2INTERSECTと呼ばれるものも同様です。