Intelは12月12日、Architecture Day 2018を開催しました。同イベントでIntelは次世代Core CPUアーキテクチャのコードネームが「SunnyCove」であることが明らかになりました。

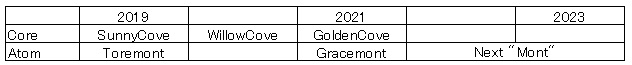

Core processorに使用される「Performance Core architecture」は3年間に3つのコードネームが並ぶ。その最初のものが「SunnyCove」で、10nmプロセスで製造され、2019年の市場投入を目指す。

「SunnyCove」の後は2020年の「WillowCove」、2021年の「GoldenCove」と続きます。

高性能CPUコアであるCore processorに加え、省電力CPUコアであるAtom processorのロードマップも明かされました。Atom系はCore系よりもややスパンが長く2019年に「Toremont」が登場した後1年おきに新コアが投入され、2021年に「Gracemont」、2023年頃にまだ名前の決まっていない次世代「~mont」が予定されています。

◇SunnyCoveのアーキテクチャの改良点

CPU core Roadmapのスライドを見ると、3つの「~Cove」には以下のように注釈がつけられていました。

SunnyCove Single-thread Performance、New ISA、Scalability Improvement

WillowCove Cache redisgn、New transitor optimization、Security Features

GoldenCove Single-thread Performance、AI performance、Network/5G、Security Features

「SunnyCove」は先にも述べられているとおり製造プロセスは10nm。Single-thread性能の向上と新たな命令セットの追加が主眼となる。

「WillowCove」は2020年予定であり、これも10nmプロセスと見込まれる。キャッシュの再設計に主眼が置かれ、L1、L2 cacheの調整が行われるのではないかとみられています。またトランジスタの最適化は製造プロセスレベルでの改良も含まれるようです。そしてセキュリティ機能の改良がこの世代で示されていました。

「GoldenCove」は2021年である。この世代になると7nmプロセスの可能性も出てきますが、不透明です。

「~Cove」最初の世代である「SunnyCove」はそのアーキテクチャの改良点もいくつか示されている。

○Frontend

・L1 date cacheの50%増量(32KB→48KB)

・L2 cacheの増量。ただし製品によって容量は異なる。

・μop cacheの増量

・2nd Level TLBの拡張

・allocation拡張(4 wide→5 wide)

・Execution Portsの増加(8→10)

・L1 Store Bandwidthを2倍に(AGUは3→4、Store Dataは1→2)

・Execution Portそのもの機能追加・拡張

「SunnyCove」と「Sklylake」のフロントエンドと対比したスライドも掲載されていましたが、「SunnyCove」では数的にも質的にも強化されているようでした。

◇Gen 11 Graphics

「SunnyCove」と組み合わされるGraphics coreがGen 11 graphicsである。Gen 11 graphicsはGT2でTFlopsレベルの性能を実現するようです。

「Kaby Lake→Coffee Lake」のiGPUはGen 9.5 graphicsとされています。Gen 9.5はGT2で24基のExecution unitを搭載。Gen 11 graphicsはGT2で64基のExecution unitを有します。64基のExecution unitは4つのスライスで構成され、1つのスライスは8基のExecution unitからなる2つのサブスライスで構成されます。

今回、IntelはGen 11 graphicsのExecution unit(EU)の中身について詳細には話されなかったものの、Gen 9.5よりも(EUあたりの?)FP16性能が2倍ほど高速化されると伝えられてます。またGPUの持つL3 cacheも3MBに増量されます。(Gen 9.5は768KB)。

◇SunnyCoveとIce Lake

Ice Lakeはどこへ行ったのか?

今回SunnyCoveのデモを行ったマザーボードをよく見るとICL-Uの文字があったようだ。ICL-UはIce Lake-Uの略です。

メディアの予測では「SunnyCove」はCore processorに使用されるCPUコア部分のコードネームで、「SunnyCove」をCPUコアとして用いたSoCなりProcessorなりのコードネームが「Ice Lake」になるのではないかと述べられています。

CPUコアそのものと製品となったSoCないしはProcessorでコードネームが異なるのはAtom系列の製品では以前よりあったことで、例えば22nmのAtomを例にとあると22nmのAtom CPUコアのコードネームは「Silvermont」でありました。しかし、それを使用したSoCのコードネームは「BayTrail」と呼ばれました。

◇3次元パッケージング技術―「Foveros」

先にAMDがCPU chipletとI/Oダイを分けた「Rome」を発表したため、そちらの方が印象が強い方もいるかもしれないが、IntelもCPUのI/OやGraphics、その他コンポーネントを分離するプランを以前より模索していた。

今回それをより推し進めるための技術として明らかにされたのが、「Foveros」です。

「Foveros」は大型のシリコンダイの上にCompute Chipやメモリやモデムが積層されており、一見するとシリコンインターポーザを使用したものに見える。しかしシリコンインターポーザは配線のためのダイでそれ自体には機能を持たないに対し、「Foveros」ではCompute Chipやメモリが載せられる「Bottom Chip」にも機能を有しており、PCHやI/Oといった機能を持たせることを考えているようです。2階建てのシリコンで1階は階段に当たる2階への出入り口と横方向の通路に加え、PCHやI/Oを備えています。そして、2階にはCPUコアやGPUコア、メモリが載る、というイメージがわかりやすいだろうか。シリコンインターポーザであれば1階は通路(配線)と階段(TSV)のみとなるようです。

「Rome」がCPU chipletを7nm、I/Oダイを14nmで製造するように、「Foveros」を用いるProcessorにおいても異なる製造プロセスの仕様が考えられている。具体的に現在「Manufactuing」となっているものが、Computeに最適化したプロセスが1274(10nm)、I/Oに最適化したものが1273(14nm)、そして、「Foveros」の「Bottom chip」はP1222と呼ばれるプロセスが用いられるようです。