AMD は、Ryzen 7000 X3D CPUに搭載されている第 2 世代 3D V-Cache テクノロジに関する追加情報をリリースしました。

AMD は、同社の 3D キャッシュの第 2 世代を明らかにし、新しいテクノロジに対する新しい最適化と機能強化

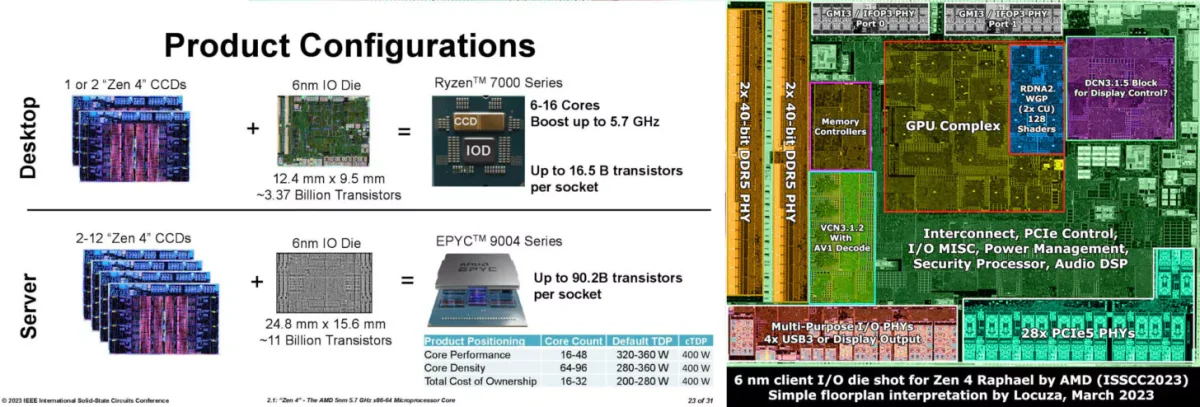

2023 年の国際固体回路会議は、同社が新しい I/O ダイに関する情報を明らかにした 2 回目のものでした。Web サイトTom’s Hardware は、 Twitter の @Locuza_ が新しいチップセットを大衆に明らかにした後、AMD から新世代に関する情報を受け取りました。

Zen 4 Raphael 6 nm client I/O die:

– 128b DDR5 PHY + 32b for ECC (8b per 32b channel)

– 2x GMI3 Ports, 3x CCDs are not possible. :p

– 28x PCIe 5, Zen1/2/3 cIOD had 32x PCIe lanes.

So AMD reduced the waste for the client market.

– Really just one RDNA2 WGP, 128 Shader "Cores" https://t.co/bkqdVvhgrn pic.twitter.com/erYxTw1p8h— Locuza (@Locuza_) March 4, 2023

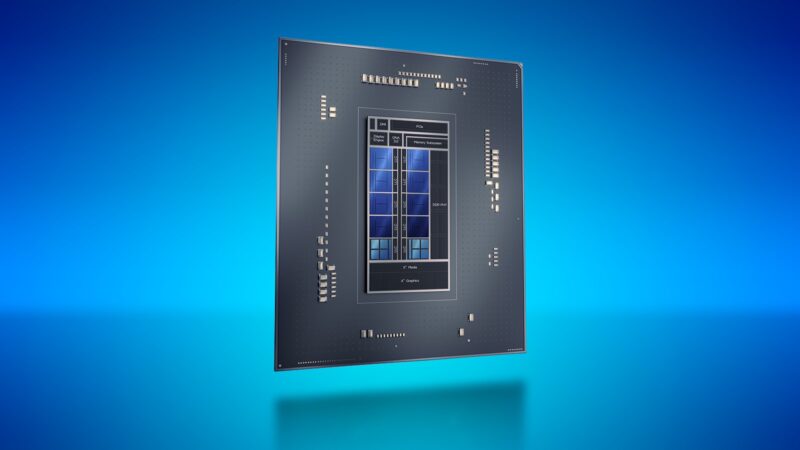

同社が公開した画像の 1 つは、次世代の 3D V-Cache 向けの新しい I/O ダイの初見でした。この新しい I/O ダイは、最新の Ryzen 7000 X3D “Raphael” CPU に搭載されています。

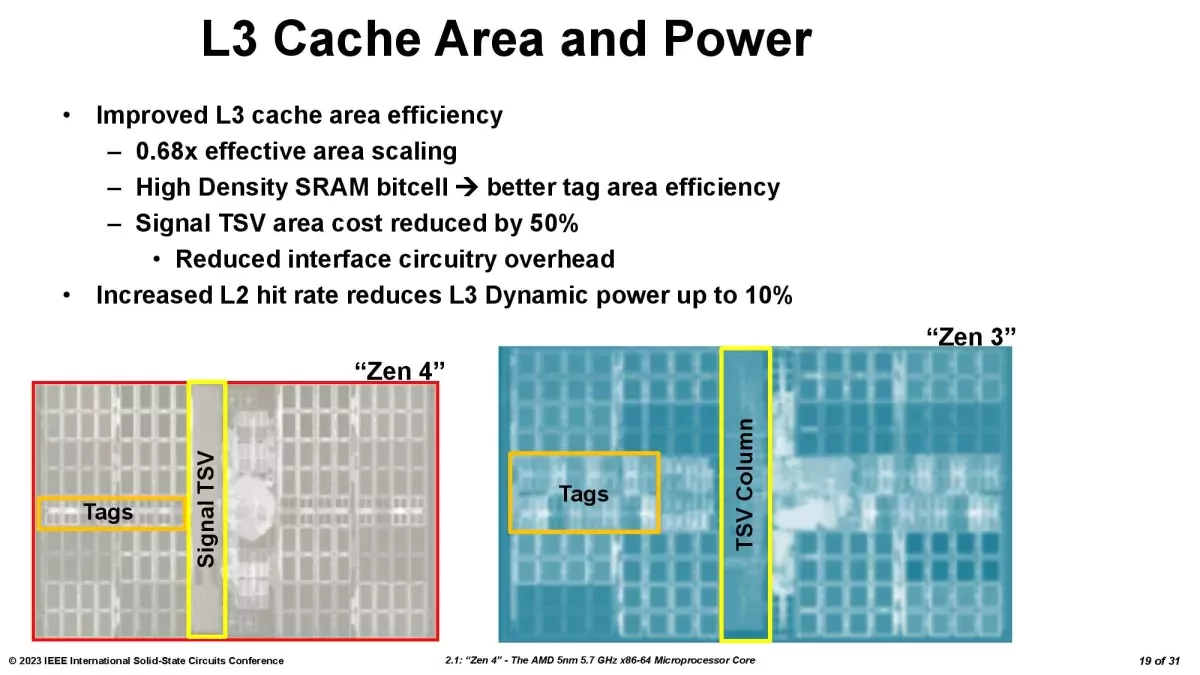

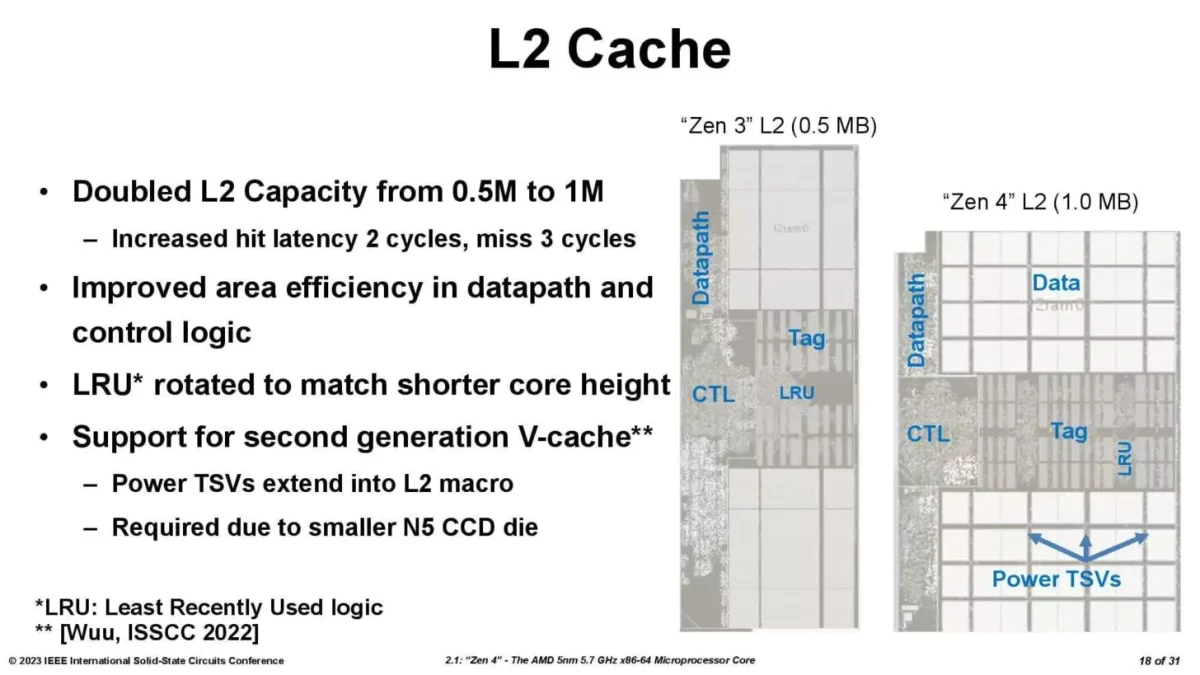

AMD は、非 X3D パーツに対して L3 キャッシュにさらに追加し、1 つのチップレットで最大 96 MB のサイズをもたらし、7nm プロセス ノード テクノロジに基づいています。L3 キャッシュは、5nm Zen 4 コア コンプレックス ダイ (CCD) 上にスタックされます。次世代のキャッシュ ダイは小さくなりますが、同じトランジスタ数が維持されます。ただし、トランジスタ密度は元の 114.6 MTr/mm² から 130.6 MTr/mm² に増加し、2.5 TB/s のより高い帯域幅に達し、5800X3D 設計から 25% の改善に相当します。

同社はThrough Silicon Vias (TSV) 接続領域を半分のサイズに調整しました。Zen 4 の CCD は現在、Ryzen 7000 X3D コンシューマ プロセッサと EPYC 9004 サーバー/ワークステーション CPU に搭載されています。現在、I/O ダイは、リリース時にコンシューマモデルとサーバー モデル用に変更され、2 つのグローバル メモリ インターコネクト ポートを備えているため、3 つの CCD を同時に使用する構成が不要になります。

新しいダイは、128 ビットの DDR5 物理層 (PHY) と、32 ビット チャネルあたり 8 ビットの 32 ビット エラー訂正コード メモリ (ECC) も提供し、PCIe 5.0 物理層の 28 倍であり、これは PCIe 5.0 よりも 4 少ない。オンデマンドの Zen 1/2/3 計算統合、または cIOD。最後に、チップレットは 128 のシェーダー コアを提供する予定です。

(Source:wccftech)

この記事へのコメントはありません。