(Source:wccftech)

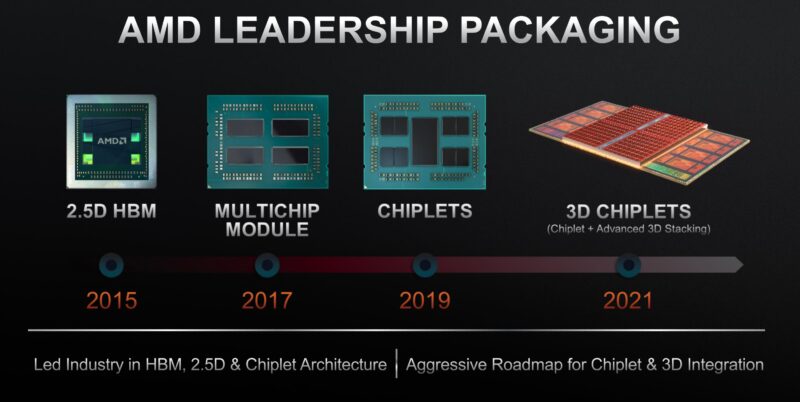

数か月前、AMDはRyzen CPUの新技術に関する情報を発表しました。AMDの3DV-Cacheテクノロジーは、最大64メガバイトの追加のL3キャッシュを使用し、Ryzen CPUの上にスタックします。

AMD 3D V-Cacheスタックチップレットデザインの詳細、ブーストされたゲームキャッシュを備えたRyzen 9 5950X

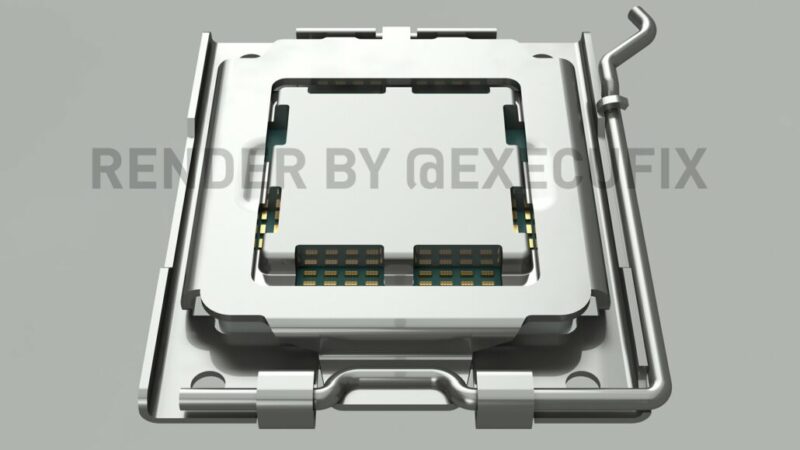

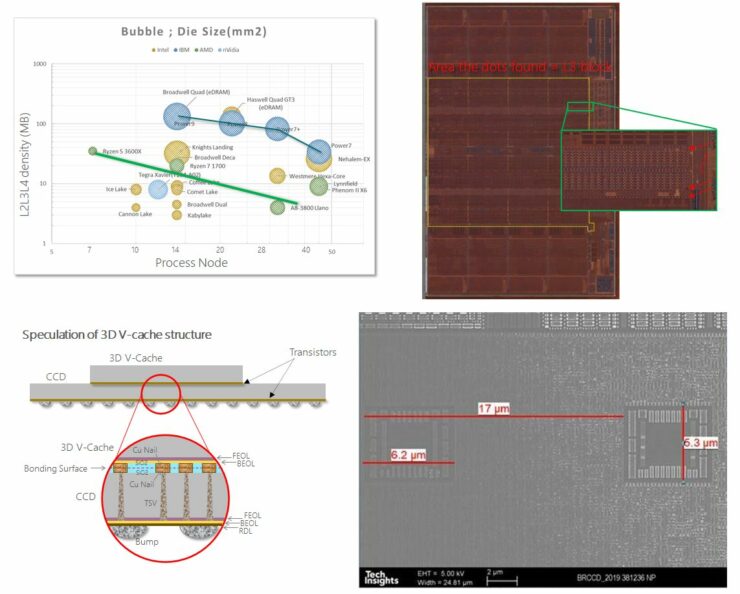

最新のAMD Zen 3 CPUのデータは、3Dキャッシュを最初からスタックできるようにするためのアクセシビリティを備えた設計を通じて示しています。これは、AMDがこのテクノロジーに数年間取り組んできたことを証明しています。現在、TechInsightsのWebサイトのFukuzaki Yuzoが、AMDのキャッシュメモリにおけるこの新しい進歩について詳しく説明しています。よく見ると、Ryzen 9 5950Xサンプルで特定の接続ポイントを見つけました。サンプルには、より多くの銅線接続ポイントを提供することで3DVキャッシュのアクセシビリティを作成する追加スペースのメモもありました。

スタッキングインストールプロセスでは、”through-silicon ” vias,(TSV)と呼ばれる技術を利用します。これは、ハイブリッドボンディングを介してSRAMの第2層をチップに接続します。TSVに通常のはんだの代わりに銅を使用すると、熱効率と帯域幅が広がります。これは、はんだを使用して2つのチップを相互に接続する代わりに使用されます。

スタッキングインストールプロセスでは、”through-silicon ” vias,(TSV)と呼ばれる技術を利用します。これは、ハイブリッドボンディングを介してSRAMの第2層をチップに接続します。TSVに通常のはんだの代わりに銅を使用すると、熱効率と帯域幅が広がります。これは、はんだを使用して2つのチップを相互に接続する代わりに使用されます。

彼はまた、LinkedInの記事でこの主題について述べています

#memory_wallの問題に対処するには、キャッシュメモリの設計が重要です。添付の画像、プロセスノード全体のキャッシュ密度の傾向のグラフをご覧ください。経済的な理由から最適なタイミングで、Logicに3Dメモリを統合することでパフォーマンスを向上させることができます。#IBM#Powerチップには大量のキャッシュと強い傾向があるを参照してください。彼らはハイエンドサーバーCPUのためにそれを行うことができます。AMDが開始した#ChipletCPU統合により、彼らは#KGD(Known Good Die)を使用して、モノリシック大規模ダイの低収量の懸念を取り除くことができます。この革新は、2022年に#IRDS(International Roadmap Devices and Systems)で期待されていました。より多くのムーアとAMDがそれを行います。

TechInsightsは、3d V-Cacheの接続方法を深く掘り下げたため、テクノロジーを逆に実行し、TSV情報や、新しい接続用のCPU内のスペースなど、次の結果を提供しました。結果は次のとおりです。

TechInsightsは、3d V-Cacheの接続方法を深く掘り下げたため、テクノロジーを逆に実行し、TSV情報や、新しい接続用のCPU内のスペースなど、次の結果を提供しました。結果は次のとおりです。

- TSVピッチ; 17μm

- KOZサイズ; 6.2×5.3μm

- TSVは概算をカウントします; 約2万3千!!

- TSVプロセス位置; M10からM11の間(M0から始まる合計15の金属)

近い将来リリースされるZen4アーキテクチャなど、AMDが将来の構造で3DV-Cacheを使用する予定があるかどうかを推測することしかできません。この新しいテクノロジーは、CPUコア数が毎年増加するにつれてL3キャッシュサイズがますます重要になるため、AMDプロセッサーにIntelテクノロジーよりも有利な飛躍をもたらします。