次世代のAlder Lake CPUファミリについて

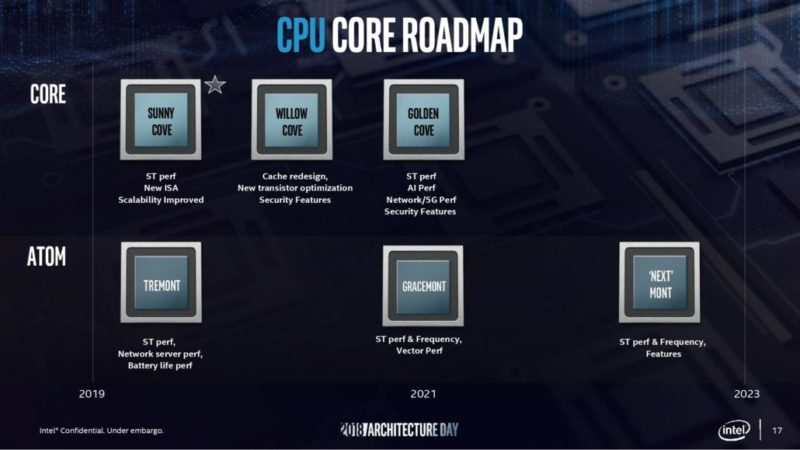

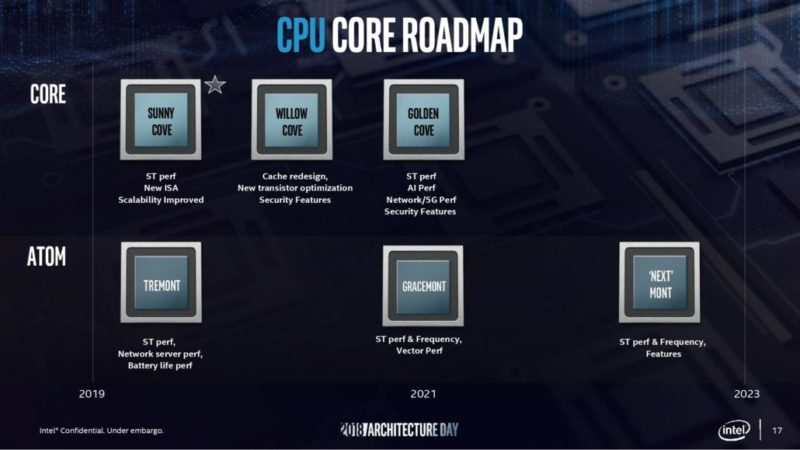

Alder Lake-S CPUの以前の詳細により、次世代デスクトップファミリは2021年後半または2022年初頭に発売されることが明らかになりました。AlderLake CPUは、ハイブリッドアーキテクチャ設計を特徴とするIntelの最初の10 nmデスクトップパーツになる可能性があります。

IntelのAlder Lake-Sは、10 nm +プロセスノード(Tiger Lake CPUの製造に使用されたのと同じノード)の進化である10nm ++プロセスノードを利用して、Intelから今まで見たものとはまったく異なります。Alder Lake-Sの第12世代コアのラインナップは、以前に報告したように大小のコアの混在をサポートする新しい設計手法を特徴としています。Alder Lake-S CPUの3つの構成がリークされました。

ご覧のとおり、CPUは最大8つの高性能コアと8つの効率最適化コアを備えたさまざまな構成を備えています。125Wのロック解除された製品と80W TDPのロックされた製品があります。いくつかのモビリティSOCが同様のコア階層を備えているのを見たので、チップ設計方法論は新しいものではありませんが、高性能デスクトップCPUラインナップで同様の結果を見るのは間違いなく興味深いものです。