(adsbygoogle = window.adsbygoogle || []).push({});

https://twitter.com/greymon55/status/1487259506723594243

https://twitter.com/greymon55/status/1487360093440000001

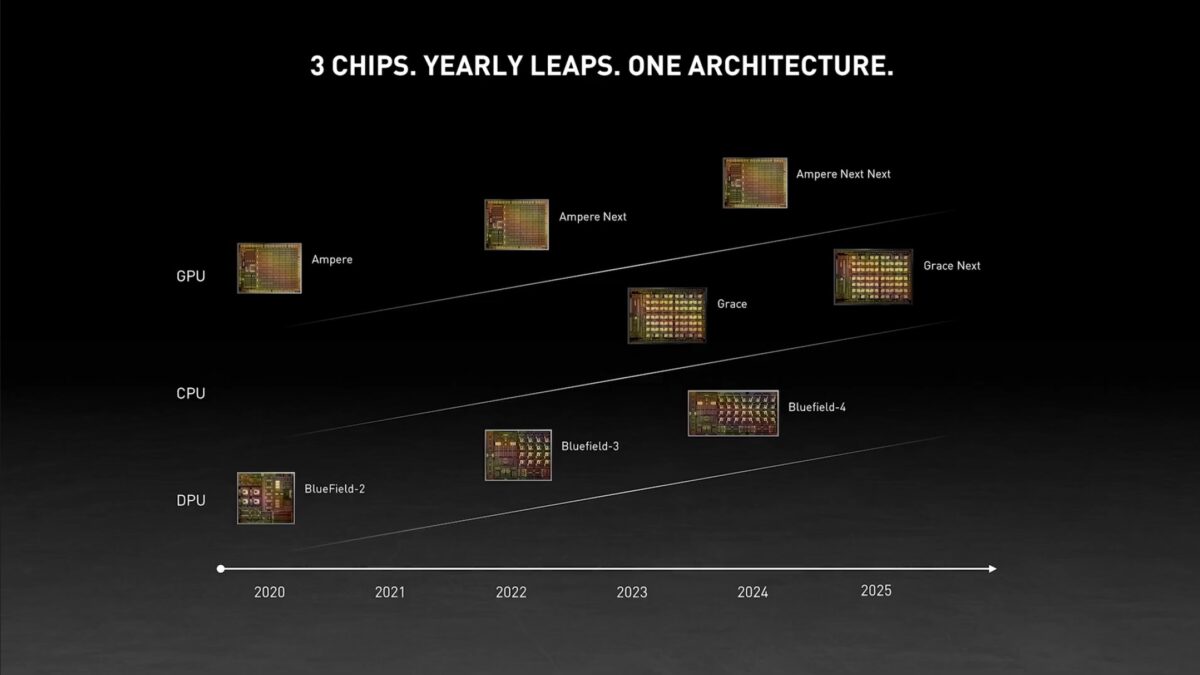

以前の情報から、NVIDIAのGH100アクセラレータはTSMCの5nmプロセスノードに基づいていることがわかります。Hopperには2つの次世代GPUモジュールがあるはずなので、合計288のSMユニットを見ています。各SMに搭載されているコアの数がわからないため、コア数の概要を示すことはできませんが、SMあたり64コアに固執する場合は、18,432コアが得られます。これは、完全なGA100GPU構成。NVIDIAは、Hopper GPU内でより多くのFP64、FP16、およびTensorコアを活用することもできます。これにより、パフォーマンスが大幅に向上します。そしてそれは、1:1FP64を搭載することが期待されているIntelのPonte Vecchioに競合するために必要になるでしょう。

最終的な構成では、各GPUモジュールで有効になっている144個のSMユニットのうち134個が付属する可能性があります。そのため、1つのGH100ダイが動作していることを確認している可能性があります。ただし、NVIDIAがGPU Sparsityを使用せずにMI200と同じFP32またはFP64フロップに到達する可能性はほとんどありません。

しかし、NVIDIAはおそらく彼らの袖に秘密兵器を持っているかもしれません、そして、それはHopperのCOPAベースのGPU実装でしょう。NVIDIAは、次世代アーキテクチャに基づく2つのドメイン専用COPA-GPUについて説明しています。1つはHPC用で、もう1つはDLセグメント用です。HPC製品は、MCM GPU設計とそれぞれのHBM / MC + HBM(IO)チップレットで構成される非常に標準的なアプローチを特徴としていますが、DL製品は物事が面白くなり始めるところです。DL製品は、GPUモジュールと相互接続された完全に独立したダイに巨大なキャッシュを収容します。

| Architecture | LLC Capacity | DRAM BW | DRAM Capacity |

|---|---|---|---|

| Configuration | (MB) | (TB/s) | (GB) |

| GPU-N | 60 | 2.7 | 100 |

| COPA-GPU-1 | 960 | 2.7 | 100 |

| COPA-GPU-2 | 960 | 4.5 | 167 |

| COPA-GPU-3 | 1920 | 2.7 | 100 |

| COPA-GPU-4 | 1920 | 4.5 | 167 |

| COPA-GPU-5 | 1920 | 6.3 | 233 |

| Perfect L2 | infinite | infinite | infinite |

最大960 / 1920MBのLLC(Last-Level-Cache)、最大233GBのHBM2eDRAM容量、および最大6.3 TB / sの帯域幅を備えたさまざまな製品が概説されています。これらはすべて理論上のものですが、NVIDIAが現在それらについて議論していることを考えると、 GTC 2022の発表で、そのような設計のHopperが見られる可能性があります。

| NVIDIA Tesla Graphics Card | Tesla K40 (PCI-Express) | Tesla M40 (PCI-Express) | Tesla P100 (PCI-Express) | Tesla P100 (SXM2) | Tesla V100 (SXM2) | NVIDIA A100 (SXM4) | NVIDIA H100 (SMX4?) |

|---|---|---|---|---|---|---|---|

| GPU | GK110 (Kepler) | GM200 (Maxwell) | GP100 (Pascal) | GP100 (Pascal) | GV100 (Volta) | GA100 (Ampere) | GH100 (Hopper) |

| Process Node | 28nm | 28nm | 16nm | 16nm | 12nm | 7nm | 5nm |

| Transistors | 7.1 Billion | 8 Billion | 15.3 Billion | 15.3 Billion | 21.1 Billion | 54.2 Billion | TBD |

| GPU Die Size | 551 mm2 | 601 mm2 | 610 mm2 | 610 mm2 | 815mm2 | 826mm2 | TBD |

| SMs | 15 | 24 | 56 | 56 | 80 | 108 | 134 (Per Module) |

| TPCs | 15 | 24 | 28 | 28 | 40 | 54 | TBD |

| FP32 CUDA Cores Per SM | 192 | 128 | 64 | 64 | 64 | 64 | 64? |

| FP64 CUDA Cores / SM | 64 | 4 | 32 | 32 | 32 | 32 | 32? |

| FP32 CUDA Cores | 2880 | 3072 | 3584 | 3584 | 5120 | 6912 | 8576 (Per Module) 17152 (Complete) |

| FP64 CUDA Cores | 960 | 96 | 1792 | 1792 | 2560 | 3456 | 4288 (Per Module)? 8576 (Complete)? |

| Tensor Cores | N/A | N/A | N/A | N/A | 640 | 432 | TBD |

| Texture Units | 240 | 192 | 224 | 224 | 320 | 432 | TBD |

| Boost Clock | 875 MHz | 1114 MHz | 1329MHz | 1480 MHz | 1530 MHz | 1410 MHz | ~1400 MHz |

| TOPs (DNN/AI) | N/A | N/A | N/A | N/A | 125 TOPs | 1248 TOPs 2496 TOPs with Sparsity | TBD |

| FP16 Compute | N/A | N/A | 18.7 TFLOPs | 21.2 TFLOPs | 30.4 TFLOPs | 312 TFLOPs 624 TFLOPs with Sparsity | 779 TFLOPs (Per Module)? 1558 TFLOPs with Sparsity (Per Module)? |

| FP32 Compute | 5.04 TFLOPs | 6.8 TFLOPs | 10.0 TFLOPs | 10.6 TFLOPs | 15.7 TFLOPs | 19.4 TFLOPs 156 TFLOPs With Sparsity | 24.2 TFLOPs (Per Module)? 193.6 TFLOPs With Sparsity? |

| FP64 Compute | 1.68 TFLOPs | 0.2 TFLOPs | 4.7 TFLOPs | 5.30 TFLOPs | 7.80 TFLOPs | 19.5 TFLOPs (9.7 TFLOPs standard) | 24.2 TFLOPs (Per Module)? (12.1 TFLOPs standard)? |

| Memory Interface | 384-bit GDDR5 | 384-bit GDDR5 | 4096-bit HBM2 | 4096-bit HBM2 | 4096-bit HBM2 | 6144-bit HBM2e | 6144-bit HBM2e |

| Memory Size | 12 GB GDDR5 @ 288 GB/s | 24 GB GDDR5 @ 288 GB/s | 16 GB HBM2 @ 732 GB/s 12 GB HBM2 @ 549 GB/s | 16 GB HBM2 @ 732 GB/s | 16 GB HBM2 @ 900 GB/s | Up To 40 GB HBM2 @ 1.6 TB/s Up To 80 GB HBM2 @ 1.6 TB/s | Up To 100 GB HBM2e @ 3.5 Gbps |

| L2 Cache Size | 1536 KB | 3072 KB | 4096 KB | 4096 KB | 6144 KB | 40960 KB | 81920 KB |

| TDP | 235W | 250W | 250W | 300W | 300W | 400W | ~450-500W |

(Source:wccftech)