(Source:Tom’s Hardware)

(Source:Tom’s Hardware)

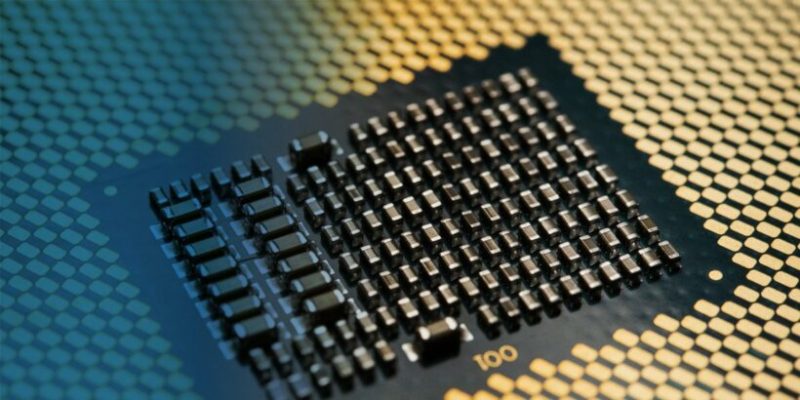

IntelのGen12に関する追加情報が公開されました。GitHubマージリクエストによると、Gen12は、Genアーキテクチャの歴史における最大のISAアップデートの1つであり、レジスタの読み取りと書き込みの間のデータコヒーレンシが除去されます。Intelはオリジナルのi965から続いてきたIntel EU ISAを最も深い部分から再構築しようとしています。再構築はほとんど全ての命令フィールド、ハードウェア実行コードそしてレジスタタイプに及び、これに統合するリクエストの更新も必要になります。しかし、最も劇的な変化はハードウェアからレジスタスコアボードロジックを除去したことです。EUはレジスタの読み込みと書き込みの間でデータのコヒーレンシを保証しません。そしてコンパイラは何時起こるかしれない潜在的なデータハザードの可能性に依存した命令に同期する必要があります。」またGen12のEUではSubsliceの単位が8から16に増量という噂もあります。

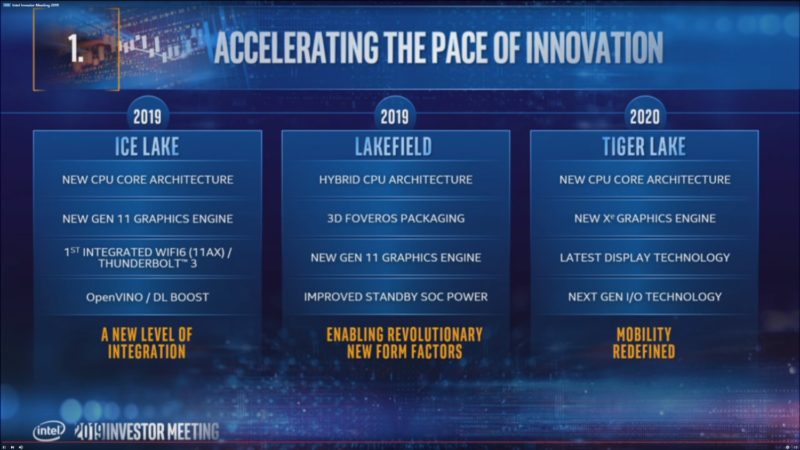

これまでの情報では、Intelからの今後のGen12(別名Xe)グラフィックスアーキテクチャに関する情報は、最近のLinuxカーネルパッチに明記されていました。特に、Gen12にはDisplay State Bufferと呼ばれる新しい表示機能があり、このエンジンは、Gen12コンテキストスイッチングを改善するものということです。

Tiger LakeとGen12グラフィックについては、前のIce Lake-U/-YでGen 11 graphicsが強力な性能を有していることが発表されている次のものになります。具体的にはTiger Lake(Ice Lake-U/-Yの次のMobile CPU、10nm)、Rocket Lake(Comet Lakeの次のCPU、14nm)、Alder Lake(Tiger LakeやRocket Lakeのさらに次。詳細不明)、Lakefield-Rに統合されると言われています。

CPU側では、Tiger Lakeに最新のWillow Coveアーキテクチャが組み込まれます。Intelは、再設計されたキャッシュ、より高い周波数(おそらく10nm ++)のトランジスタ最適化、およびさらなるセキュリティ機能を搭載するとのことです。